# AN10039

# ISP1582/83 Firmware Programming Guide

Rev. 02 — 3 January 2005

Application note

#### **Document information**

| Info     | Content                                                            |

|----------|--------------------------------------------------------------------|

| Keywords | isp1582; isp1583; peripheral controller; usb; universal serial bus |

| Abstract | This document explains the firmware programming of the ISP1582/83. |

#### **Revision history**

| Rev | Date     | Description                          |

|-----|----------|--------------------------------------|

| 2.0 | 20050103 | Second release: updated Section 2.6. |

| 1.0 | 20040603 | First release.                       |

# **Contact information**

For additional information, please visit: <u>http://www.semiconductors.philips.com</u> For sales office addresses, please send an email to: <u>sales.addresses@www.semiconductors.philips.com</u>

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

## 1. Introduction

The ISP1582/83 is a Hi-Speed Universal Serial Bus (USB) peripheral controller that provides a flexible interface for a wide range of microcontrollers. The high-speed microcontroller interface increases system throughput and reduces processor utilization.

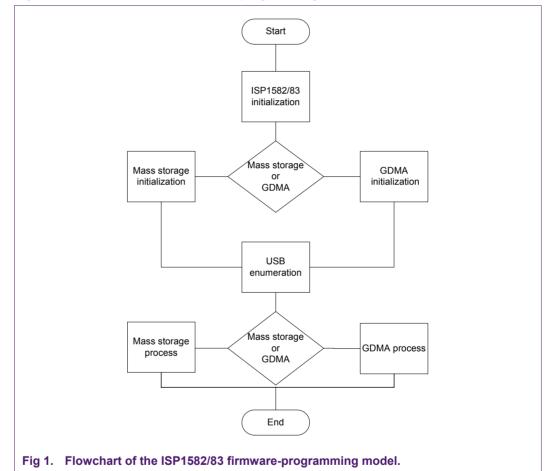

The ISP1582/83 can be configured to function, with a common USB bus enumeration process, as a Generic Direct Memory Access (GDMA) application or a mass storage application. This document is divided based on the USB enumeration and the two supported applications.

Fig 1 shows the ISP1582/83 firmware-programming model.

# 2. ISP1582/83 initialization routine

## 2.1 Initializing the ISP1582/83 registers

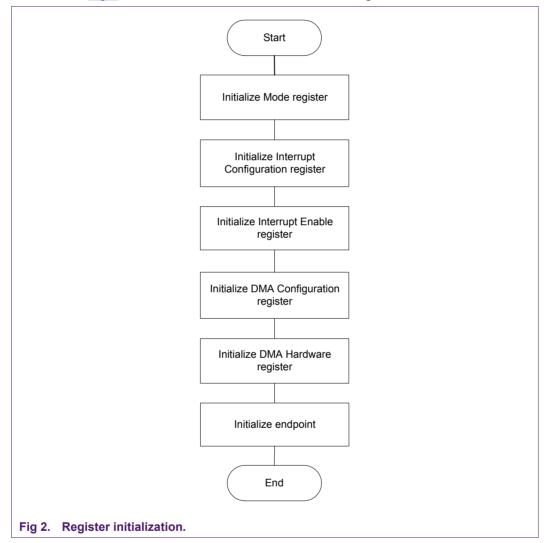

The initialization routine depends on the application targeted for the ISP1582/83. The routine has most of the initializations common to all applications, except for the DMA Configuration and DMA Hardware registers that determine the function of the ISP1582/83. Fig 2 shows the flowchart of the ISP1582/83 register initialization.

## 2.2 Initializing the Mode register

After the power-on reset, the processor initializes the Mode register (see <u>Table 1:</u>). This register can be programmed, depending on the user application.

| l able 1: | Mode register: | bit allocation |        |         |           |        |              |           |

|-----------|----------------|----------------|--------|---------|-----------|--------|--------------|-----------|

| Bit       | 15             | 14             | 13     | 12      | 11        | 10     | 9            | 8         |

| Symbol    | TEST2          | TEST1          | TEST0  |         | reserved  |        | DMACLK<br>ON | VBUSSTAT  |

| Reset     | -              | -              | -      | -       | -         | -      | 0            | -         |

| Bus reset | -              | -              | -      | -       | -         | -      | 0            | -         |

| Access    | R              | R              | R      | R       | R         | R      | R/W          | R         |

| Bit       | 7              | 6              | 5      | 4       | 3         | 2      | 1            | 0         |

| Symbol    | CLKAON         | SNDRSU         | GOSUSP | SFRESET | GLINTENA  | WKUPCS | PWRON        | SOFTCT    |

| Reset     | 0              | 0              | 0      | 0       | 0         | 0      | 0            | 0         |

| Bus reset | 0              | 0              | 0      | 0       | unchanged | 0      | 0            | unchanged |

| Access    | R/W            | R/W            | R/W    | R/W     | R/W       | R/W    | R/W          | R/W       |

#### Table 1: Mode register: bit allocation

The DMACLKON bit of the Mode register determines whether the clock should be supplied to the DMA core of the ISP1582/83. Disabling the bit at initialization saves power. The DMA clock can be switched on when DMA is required using the DMACLKON bit.

Power can also be saved by disabling clock CLKAON during suspend mode. It is recommended that you use this power saving mechanism to save power when the ISP1582/83 is configured to bus-powered applications. Next, set the global interrupt enable (bit GLINTENA) to enable the interrupt mechanism of the ISP1582/83. The ISP1582/83 allows you to wake up the system from suspend mode by toggling the chip select (pin CS\_N) of the ISP1582/83.

The ISP1582/83 allows you to design systems to support the sleep mode in which power to the ISP1582/83 is turned off to save power. The PWRON bit in the Mode register configures the ISP1582/83 into two modes of operation when it is in the suspend state. When the bit is set to logic 0, the firmware must issue an unlock command to the ISP1582/83 before any write operation to a register can be performed. This prevents accidental writing to registers when the processor wakes up from the power saving mode.

The SoftConnect<sup>TM</sup> feature (bit SOFTCT) is used to connect the pull-up resistor to the DP line of the ISP1582/83. This gives the users complete authority on when to connect and disconnect from the USB bus. The SOFTCT bit is used together with V<sub>BUS</sub> (bit VBUSSTAT) that reflects whether the USB cable is plugged in or out.

## 2.3 Initializing the Interrupt Configuration register

After setting the Mode register, the Interrupt Configuration register (see <u>Table 2</u>:) is initialized. This register controls how an interrupt is generated for the control pipe, IN endpoint and OUT endpoint.

| Bit       | 7     | 6        | 5     | 4         | 3      | 2         | 1         | 0         |

|-----------|-------|----------|-------|-----------|--------|-----------|-----------|-----------|

| Symbol    | CDBGN | 10D[1:0] | DDBGM | DDIN[1:0] | DDBGMO | DOUT[1:0] | INTLVL    | INTPOL    |

| Reset     | 1     | 1        | 1     | 1         | 1      | 1         | 0         | 0         |

| Bus reset | 1     | 1        | 1     | 1         | 1      | 1         | unchanged | unchanged |

| Access    | R/W   | R/W      | R/W   | R/W       | R/W    | R/W       | R/W       | R/W       |

#### Table 2: Interrupt Configuration register: bit allocation

The interrupt generation depends on the type of mode setting specified in the register; see <u>Table 3</u>: CDBGMOD is for the control pipe, DDBGMODIN is for the IN pipe, and DDBGMODOUT is for the OUT pipe. The register sets interrupt to the level or pulse trigger by using the INTLVL bit. The polarity of the interrupt signal is control by INTPOL.

| Table 3: | Debug mode settings                |                                    |                                          |

|----------|------------------------------------|------------------------------------|------------------------------------------|

| Value    | CDBGMOD                            | DDBGMODIN                          | DDBGMODOUT                               |

| 00h      | Interrupt on all ACK and NAK       | Interrupt on all ACK and NAK       | Interrupt on all ACK, NYET and NAK       |

| 01h      | Interrupt on all ACK               | Interrupt on ACK                   | Interrupt on ACK and NYET                |

| 1Xh      | Interrupt on all ACK and first NAK | Interrupt on all ACK and first NAK | Interrupt on all ACK, NYET and first NAK |

The typical function of the Interrupt Configuration register is to enable the ACK interrupt.

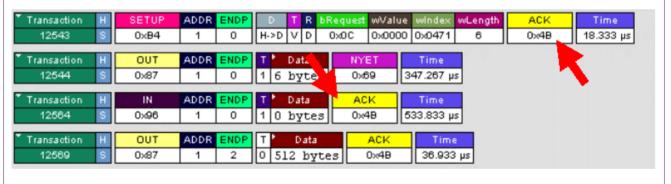

The following figures show the CATC trace of the ACK interrupt with the red arrows indicating the interrupt signal that will be generated on the INT pin, when ACK condition occurs.

#### Fig 3. CATC capture of setup and OUT ACK interrupt.

The following sample code programs the IN endpoint interrupt to all ACK conditions:

```

Void Init_D14_SFR(void)

{

//Set the control pipe to ACK only interrupt

//Set the IN pipe to ACK only interrupt

//Set OUT pipe to ACK and NYET interrupt

D14_Cntrl_Reg.D14_INT_CONFIG = 0x54;

}

```

ISP1582/83 Firmware Programming Guide

| Transaction | H | SETUP | ADDR | ENDP | D    | Ŧ   | R   | bRequest | wValue | windex          | wLength | ACK  | Time      |

|-------------|---|-------|------|------|------|-----|-----|----------|--------|-----------------|---------|------|-----------|

| 13408       | S | 0×84  | 1    | 0    | H->D | V   | D   | 0%00     | 0x0000 | 0x0471          | 6       | 0×48 | 16.833 µs |

| Transaction | Н | PING  | ADDR | ENDP | A    | ск  |     | Time     |        |                 |         |      |           |

| 13409       | S | 0x2D  | 1    | 0    | 0>   | ¢48 |     | 15.933   | μs     |                 |         |      |           |

| Transaction | Н | OUT   | ADDR | ENDP | Т    | Da  | ta  | NY       | ET     | Time            |         |      |           |

| 13410       | S | 0x87  | 1    | 0    | 16   | by  | te: | s Oxt    | 39 3   | 86.167 µ        | s       |      |           |

| Transaction | Н | IN    | ADDR | ENDP | Т    | Da  | ta  | AC       | K      | Time            |         |      |           |

| 13433       | 8 | 0×96  | 1    | 0    | 10   | by  | te: | 3 0×4    | 4B     | 9 <b>1</b> 67 µ | s       |      |           |

| Transaction | Н | IN    | ADDR | ENDP | T    | D   | ata |          | ACK    | Time            | 2       |      |           |

| 13437       | S | 0%96  | 1    | 2    | 0 51 | 12  | by  | tes      | 0×48   | 39.067          | μs      |      |           |

| Transaction | Н | IN    | ADDR | ENDP | т    | D   | ata |          | ACK    | Time            | •       |      |           |

| 13439       | S | 0%96  | 1    | 2    | 1 51 | 12  | by  | tes      | 0x4B   | 28.000          | ) µs    |      |           |

#### Fig 4. CATC capture of IN ACK interrupt.

The OUT endpoint is programmed to all ACK and NYET interrupts as shown in Fig 5.

| Transaction |        | ADDR ENDP | T Data ACK Time                               |

|-------------|--------|-----------|-----------------------------------------------|

|             | 0%87   | 1 2       | 1 512 bytes 0x48 88.100 µs                    |

| Transaction | OUT    | ADDR ENDP | T Data ACK Time                               |

| 12614       | 0x87   | 1 2       | 0 512 bytes 0x48 19.567 µs                    |

| Transaction | I OUT  | ADDR ENDP | T Data NYET Time                              |

| 12615       | 0x87   | 1 2       | 1 128 bytes 0x69 98.968 ms                    |

| Transaction | SETUP  | ADDR ENDP | D T R bRequest wValue windex wLength ACK Time |

| 13408       | 0×84   | 1 0       | H->D V D 0x0C 0x0000 0x0471 6 0x48 16.833     |

| Transaction | H PING | ADDR ENDP | ACK Time                                      |

| 13409       | 0x2D   | 1 0       | 0x4B 15.933 µs                                |

|             |        |           |                                               |

#### Fig 5. CATC capture of OUT ACK interrupt.

## 2.4 Initializing the Interrupt Enable register

Next is the initialization of the Interrupt Enable register (see <u>Table 4</u>:). Setting the respective bit to logic 1 will enable the interrupt signal to be generated on the INT pin of the ISP1582/83. Take into consideration the interrupt service routine because an AND operation must be performed on the bits in the Interrupt Reason register with the enable interrupt. The Interrupt Reason register reflects the status bit of the respective event, even if the enable bit is not set in the Interrupt Enable register.

| i able 4. | interrupt Enable | e register. D | it anocation |        |        |        |          |               |

|-----------|------------------|---------------|--------------|--------|--------|--------|----------|---------------|

| Bit       | 31               | 30            | 29           | 28     | 27     | 26     | 25       | 24            |

| Symbol    |                  |               | resei        | rved   |        |        | IEP7TX   | IEP7RX        |

| Reset     | -                | -             | -            | -      | -      | -      | 0        | 0             |

| Bus reset | -                | -             | -            | -      | -      | -      | 0        | 0             |

| Access    | -                | -             | -            | -      | -      | -      | R/W      | R/W           |

| Bit       | 23               | 22            | 21           | 20     | 19     | 18     | 17       | 16            |

| Symbol    | IEP6TX           | IEP6RX        | IEP5TX       | IEP5RX | IEP4TX | IEP4RX | IEP3TX   | IEP3RX        |

| Reset     | 0                | 0             | 0            | 0      | 0      | 0      | 0        | 0             |

| Bus reset | 0                | 0             | 0            | 0      | 0      | 0      | 0        | 0             |

| Access    | R/W              | R/W           | R/W          | R/W    | R/W    | R/W    | R/W      | R/W           |

| Bit       | 15               | 14            | 13           | 12     | 11     | 10     | 9        | 8             |

| Symbol    | IEP2TX           | IEP2RX        | IEP1TX       | IEP1RX | IEP0TX | IEP0RX | reserved | IEP0<br>SETUP |

| Reset     | 0                | 0             | 0            | 0      | 0      | 0      | -        | 0             |

| Bus reset | 0                | 0             | 0            | 0      | 0      | 0      | -        | 0             |

| Access    | R/W              | R/W           | R/W          | R/W    | R/W    | R/W    | R/W      | R/W           |

| Bit       | 7                | 6             | 5            | 4      | 3      | 2      | 1        | 0             |

| Symbol    | IEVBUS           | IEDMA         | IEHS_STA     | IERESM | IESUSP | IEPSOF | IESOF    | IEBRST        |

| Reset     | 0                | 0             | 0            | 0      | 0      | 0      | 0        | 0             |

| Bus reset | 0                | 0             | 0            | 0      | 0      | 0      | 0        | unchanged     |

| Access    | R/W              | R/W           | R/W          | R/W    | R/W    | R/W    | R/W      | R/W           |

#### Table 4: Interrupt Enable register: bit allocation

The following is a sample code for the interrupt service routine:

```

Void Int_Ext_0(void) interrupt 0 using 1

{

// Read in USB interrupt reason register

USB_Int_Flag.VALUE = D14_Cntrl_Reg.D14_INT.VALUE;

USB_Int_Flag.VALUE &= D14_INT_ENABLE;

//Read in DMA interrupt register

DMA_Int_Flag.VALUE = D14_Cntrl_Reg.D14_DMA_INT.VALUE;

DMA_Int_Flag.VALUE &= D14_DMA_INT_ENABLE;

//Clear DMA interrupt register

D14_Cntrl_Reg.D14_DMA_INT.VALUE = DMA_Int_Flag.VALUE;

// Clear USB interrupt reason register

D14_Cntrl_Reg.D14_INT.VALUE = USB_Int_Flag.VALUE;

}

```

## 2.5 Initializing the DMA Configuration and Hardware registers

Next, you configure the DMA Configuration register (see <u>Table 5</u>:) and DMA Hardware register (see <u>Table 6</u>:) to either GDMA or mass storage application. Based on the application, some associated registers must be programmed.

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

| Table 5:  | DMA Configurati  | on registe | r: bit allocation |       |          |        |               |       |  |

|-----------|------------------|------------|-------------------|-------|----------|--------|---------------|-------|--|

| Bit       | 15               | 14         | 13                | 12    | 11       | 10     | 9             | 8     |  |

| Symbol    | reserved         |            | ATA_<br>MODE      | DMA_M | ODE[1:0] | F      | PIO_MODE[2:0] |       |  |

| Reset     | 0                | 0          | 0                 | 0     | 0        | 0      | 0             | 0     |  |

| Bus reset | 0                | 0          | 0                 | 0     | 0        | 0      | 0             | 0     |  |

| Access    | R/W              | R/W        | R/W               | R/W   | R/W      | R/W    | R/W           | R/W   |  |

| Bit       | 7                | 6          | 5                 | 4     | 3        | 2      | 1             | 0     |  |

| Symbol    | DIS_XFER<br>_CNT |            | reserved          |       | MOD      | E[1:0] | reserved      | WIDTH |  |

| Reset     | 0                | 0          | 0                 | 0     | 0        | 0      | 0             | 1     |  |

| Bus reset | 0                | 0          | 0                 | 0     | 0        | 0      | 0             | 1     |  |

| Access    | R/W              | R/W        | R/W               | R/W   | R/W      | R/W    | R/W           | R/W   |  |

|           |                  |            |                   |       |          |        |               |       |  |

## Table 5: DMA Configuration register: bit allocation

#### Table 6: DMA Hardware register: bit allocation

| Bit       | 7     | 6      | 5       | 4      | 3       | 2            | 1             | 0        |

|-----------|-------|--------|---------|--------|---------|--------------|---------------|----------|

| Symbol    | ENDIA | N[1:0] | EOT_POL | MASTER | ACK_POL | DREQ_<br>POL | WRITE_<br>POL | READ_POL |

| Reset     | 0     | 0      | 0       | 0      | 0       | 1            | 0             | 0        |

| Bus reset | 0     | 0      | 0       | 0      | 0       | 1            | 0             | 0        |

| Access    | R/W   | R/W    | R/W     | R/W    | R/W     | R/W          | R/W           | R/W      |

The ISP1582/83 can be configured to various operation modes, depending on the combination of the various bits in the DMA Configuration and DMA Hardware registers. <u>Table 7:</u> illustrates the valid combinations.

#### Table 7: DMA configuration

| ATA mode | Master | DMA mode | PIO mode | DIS_XFER<br>_CNT | Mode | Width | Description                                                                                               |

|----------|--------|----------|----------|------------------|------|-------|-----------------------------------------------------------------------------------------------------------|

| 0        | 0      | Not used | Not used | 0                | 0    | 1     | GDMA Slave mode<br>DMA Transfer Counter<br>DIOR as read strobe<br>DIOW as write strobe<br>16-bit data bus |

|          |        | Not used | Not used | 0                | 1    | 1     | GDMA Slave mode<br>DMA Transfer Counter<br>DIOR as read strobe<br>DACK as write strobe<br>16-bit data bus |

|          |        | Not used | Not used | 0                | 2    | 1     | GDMA Slave mode<br>DMA Transfer Counter<br>DACK as read strobe<br>DACK as write strobe<br>16-bit data bus |

# ISP1582/83 Firmware Programming Guide

AN10039

# AN10039

**Philips Semiconductors**

## ISP1582/83 Firmware Programming Guide

| ATA mode | Master | DMA mode | PIO mode | DIS_XFER<br>_CNT | Mode     | Width | Description                                                                                              |

|----------|--------|----------|----------|------------------|----------|-------|----------------------------------------------------------------------------------------------------------|

|          |        | Not used | Not used | 0                | 0        | 0     | GDMA Slave mode<br>DMA Transfer Counter<br>DIOR as read strobe<br>DIOW as write strobe<br>8-bit data bus |

|          |        | Not used | Not used | 0                | 1        | 0     | GDMA Slave mode<br>DMA Transfer Counter<br>DIOR as read strobe<br>DACK as write strobe<br>8-bit data bus |

|          |        | Not used | Not used | 0                | 2        | 0     | GDMA Slave mode<br>DMA Transfer Counter<br>DACK as read strobe<br>DACK as write strobe<br>8-bit data bus |

|          |        | Not used | Not used | 1                | 2        | 0     | GDMA Slave mode<br>EOT mode<br>DACK as read strobe<br>DACK as write strobe<br>8-bit data bus             |

| 1        | 0      | 0        | 0        | Not used         | Not used | 1     | ATA mode<br>MDMA Mode 0 strobe timing<br>PIO mode 0 timing                                               |

|          |        | 1        | 1        | Not used         | Not used | 1     | ATA mode<br>MDMA Mode 1 strobe timing<br>PIO Mode 1 timing                                               |

|          |        | 2        | 2        | Not used         | Not used | 1     | ATA mode<br>MDMA Mode 2 strobe timing<br>PIO Mode 2 timing                                               |

|          |        | 2        | 3        | Not used         | Not used | 1     | ATA mode<br>MDMA Mode 2 strobe timing<br>PIO Mode 3 timing                                               |

|          |        | 2        | 4        | Not used         | Not used | 1     | ATA mode<br>MDMA Mode 2 strobe timing<br>PIO Mode 4 timing                                               |

| 1        | 1      | Not used | Not used | Not used         | 0        | 1     | GDMA Master mode<br>DMA Transfer Counter<br>ATA MDMA 0 Strobe timing<br>16-bit data bus                  |

|          |        | Not used | Not used | Not used         | 1        | 1     | GDMA Master mode<br>DMA Transfer Counter<br>ATA MDMA 1 Strobe timing<br>16-bit data bus                  |

|          |        | Not used | Not used | Not used         | 2        | 1     | GDMA Master mode<br>DMA Transfer Counter<br>ATA MDMA 2 Strobe timing<br>16-bit data bus                  |

ISP1582/83 Firmware Programming Guide

| ATA mode | Master | DMA mode | PIO mode | DIS_XFER<br>_CNT | Mode    | Width   | Description                                                                            |

|----------|--------|----------|----------|------------------|---------|---------|----------------------------------------------------------------------------------------|

|          |        | Not used | Not used | Not used         | 0       | 0       | GDMA Master mode<br>DMA Transfer Counter<br>ATA MDMA 0 Strobe timing<br>8-bit data bus |

|          |        | Not used | Not used | Not used         | 1       | 0       | GDMA Master mode<br>DMA Transfer Counter<br>ATA MDMA 1 Strobe timing<br>8-bit data bus |

|          |        | Not used | Not used | Not used         | 2       | 0       | GDMA Master mode<br>DMA Transfer Counter<br>ATA MDMA 2 Strobe timing<br>8-bit data bus |

| 0        | 1      | Invalid  | Invalid  | Invalid          | Invalid | Invalid | Invalid Mode                                                                           |

When DIS\_XFER\_CNT is set to logic 1, the DMA transfer counter is not in use, and the DMA termination is done using the input signal of pin EOT. This mode is called the EOT mode. The polarity of pin EOT can be set using the EOT\_POL bit in the DMA Hardware register.

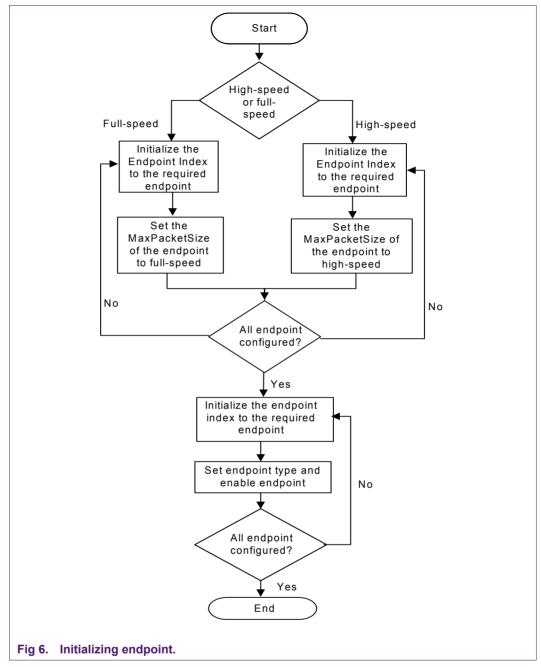

## 2.6 Initializing the ISP1582/83 endpoint

The endpoint FIFO configuration is done using the Endpoint MaxPacketSize register (see <u>Table 8:</u>) and the Endpoint Type register (<u>Table 9:</u>), and indexed using the Endpoint Index register (see <u>Table 10:</u>).

For the same endpoint number, ensure that initialization is done for both the IN and OUT, even if only one side is used.

| Bit       | 15       | 14  | 13  | 12    | 11      | 10          | 9   | 8   |

|-----------|----------|-----|-----|-------|---------|-------------|-----|-----|

| Symbol    | reserved |     |     | NTRAN | IS[1:0] | FFOSZ[10:8] |     |     |

| Reset     | -        | -   | -   | 0     | 0       | 0           | 0   | 0   |

| Bus reset | -        | -   | -   | 0     | 0       | 0           | 0   | 0   |

| Access    | R/W      | R/W | R/W | R/W   | R/W     | R/W         | R/W | R/W |

| Bit       | 7        | 6   | 5   | 4     | 3       | 2           | 1   | 0   |

| Symbol    |          |     |     | FFOS  | Z[7:0]  |             |     |     |

| Deast     |          |     |     |       |         |             |     |     |

| Reset     | 0        | 0   | 0   | 0     | 0       | 0           | 0   | 0   |

| Bus reset | 0        | 0   | 0   | 0     | 0       | 0           | 0   | 0   |

#### Table 8: Endpoint MaxPacketSize register: bit allocation

| Table 5.  | -nupoint Type | register. Dit a | nocation |         |        |        |       |         |

|-----------|---------------|-----------------|----------|---------|--------|--------|-------|---------|

| Bit       | 15            | 14              | 13       | 12      | 11     | 10     | 9     | 8       |

| Symbol    |               |                 |          | rese    | rved   |        |       |         |

| Reset     | -             | -               | -        | -       | -      | -      | -     | -       |

| Bus reset | -             | -               | -        | -       | -      | -      | -     | -       |

| Access    | R/W           | R/W             | R/W      | R/W     | R/W    | R/W    | R/W   | R/W     |

| Bit       | 7             | 6               | 5        | 4       | 3      | 2      | 1     | 0       |

| Symbol    |               | reserved        |          | NOEMPKT | ENABLE | DBLBUF | ENDPT | YP[1:0] |

| Reset     | -             | -               | -        | 0       | 0      | 0      | 0     | 0       |

| Bus reset | -             | -               | -        | 0       | 0      | 0      | 0     | 0       |

| Access    | R/W           | R/W             | R/W      | R/W     | R/W    | R/W    | R/W   | R/W     |

|           |               |                 |          |         |        |        |       |         |

#### Table 9: Endpoint Type register: bit allocation

#### Table 10: Endpoint Index register: bit allocation

| Bit       | 7                 | 6   | 5   | 4            | 3   | 2   | 1   | 0   |

|-----------|-------------------|-----|-----|--------------|-----|-----|-----|-----|

| Symbol    | reserved EP0SETUP |     |     | ENDPIDX[3:0] |     |     |     |     |

| Reset     | -                 | -   | 0   | 0            | 0   | 0   | 0   | 0   |

| Bus reset | -                 | -   | 0   | 0            | 0   | 0   | 0   | 0   |

| Access    | R/W               | R/W | R/W | R/W          | R/W | R/W | R/W | R/W |

Initialization of the endpoint is done as depicted by the flowchart in Fig 6.

#### ISP1582/83 Firmware Programming Guide

N10039

The initialization routine is used when:

- The system is powered up.

- A bus-reset event occurs.

- There is a change from full-speed to high-speed.

The following is a sample code for endpoint initialization:

```

void Init_Endpoint(void)

{

//check if device in full speed state

if(Kernel_Flag.BITS.HS_FS_State == FULL_SPEED)

```

## AN10039 ISP1582/83 Firmware Programming Guide

```

//Bulk Out MaxPacketSize Endpoint

D14 Cntrl Reg.D14 ENDPT INDEX = 4;

D14 Cntrl Reg.D14 ENDPT MAXPKTSIZE.VALUE = 0x4000;

//Bulk In MaxPacketSize Endpoint

D14 Cntrl Req.D14 ENDPT INDEX = 5;

D14 Cntrl Reg.D14 ENDPT MAXPKTSIZE.VALUE = 0x4000;

//Bulk Out Endpoint Type

D14 Cntrl Req.D14 ENDPT INDEX = 4;

D14 Cntrl Req.D14 ENDPT TYPE.VALUE = 0x1600;

//Bulk In Endpoint Type

D14 Cntrl Reg.D14 ENDPT INDEX = 5;

D14 Cntrl Reg.D14 ENDPT TYPE.VALUE = 0x1600;

//enable FIFO

D14 Cntrl Reg.D14 ENDPT INDEX = 4;

D14 Cntrl Reg.D14 ENDPT TYPE.VALUE = 0x0800;

//enable FIFO

D14 Cntrl Reg.D14 ENDPT INDEX = 5;

D14 Cntrl Reg.D14 ENDPT TYPE.VALUE | = 0x0800;

}

//check if device in high speed

if (Kernel Flag.BITS.HS FS State == HIGH SPEED)

{

//Bulk Out MaxPacketSize Endpoint

D14 Cntrl Reg.D14 ENDPT INDEX = 4;

D14_Cntrl_Reg.D14_ENDPT_MAXPKTSIZE.VALUE = 0x0002;

//Bulk In MaxPacketSize Endpoint

D14 Cntrl Reg.D14 ENDPT INDEX = 5;

D14 Cntrl Reg.D14 ENDPT MAXPKTSIZE.VALUE = 0x0002;

//Bulk Out Endpoint Type

D14 Cntrl Reg.D14 ENDPT INDEX = 4;

D14 Cntrl Reg.D14 ENDPT TYPE.VALUE = 0x1600;

//Bulk In Endpoint Type

D14 Cntrl Reg.D14 ENDPT INDEX = 5;

D14 Cntrl Reg.D14 ENDPT TYPE.VALUE = 0x1600;

//enable FIFO

D14 Cntrl Reg.D14 ENDPT INDEX = 4;

D14 Cntrl Reg.D14 ENDPT TYPE.VALUE | = 0x0800;

//enable FIFO

D14 Cntrl Reg.D14 ENDPT INDEX = 5;

```

D14\_Cntrl\_Reg.D14\_ENDPT\_TYPE.VALUE |= 0x0800;

The initialization of the endpoint is done as shown in  $\underline{Fig 2}$  to allow the endpoint FIFO RAM to be configured. Ensure that the total endpoints FIFO size does not exceed 8 kB.

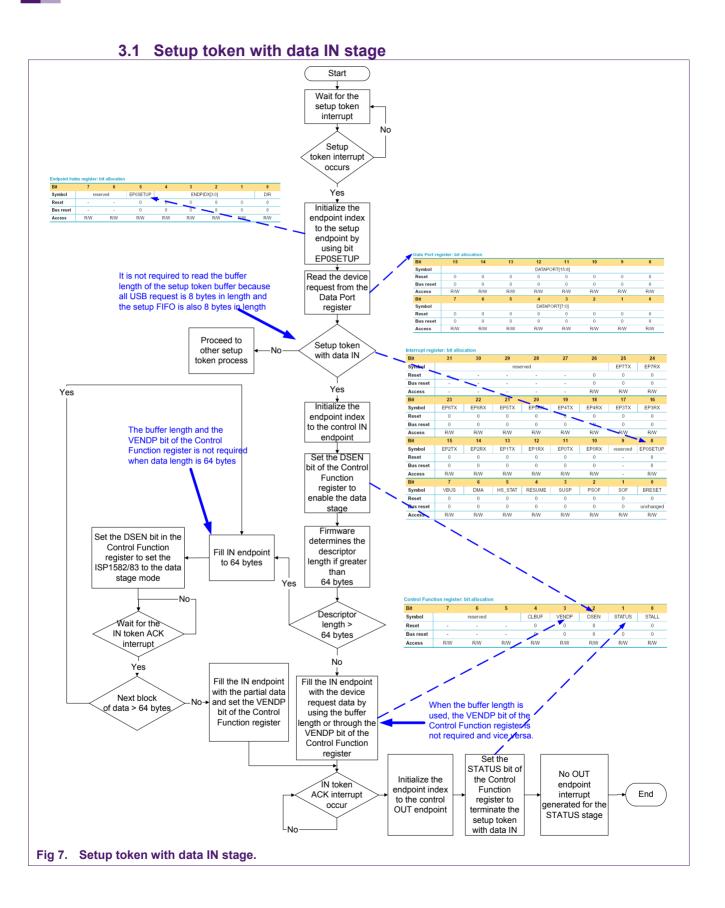

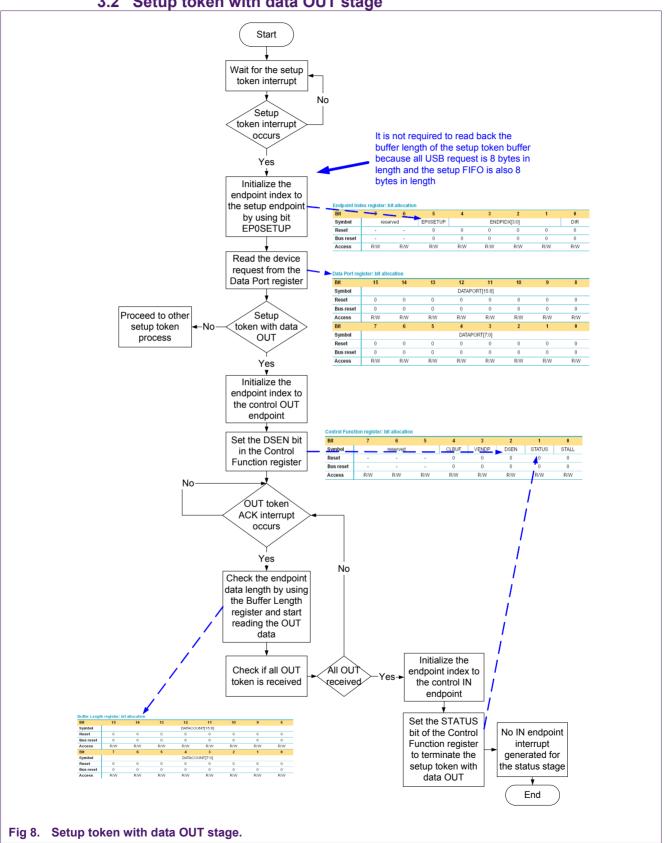

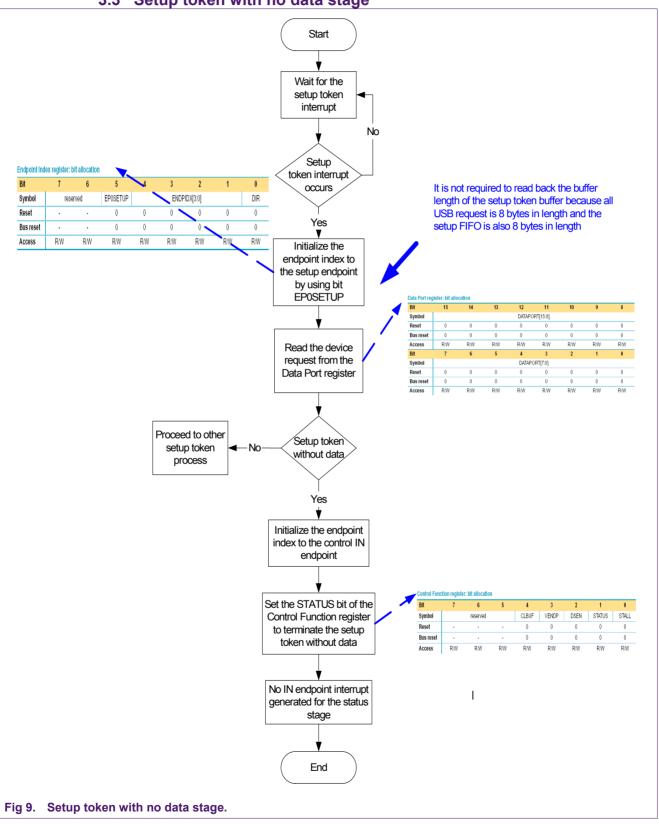

## 3. ISP1582/83 USB enumeration process

The USB enumeration process can be divided into three categories:

- Setup token with data IN stage; see Section 3.1

- Setup token with data OUT stage; see <u>Section 3.2</u>

- Setup token with no data stage; see <u>Section 3.3</u>.

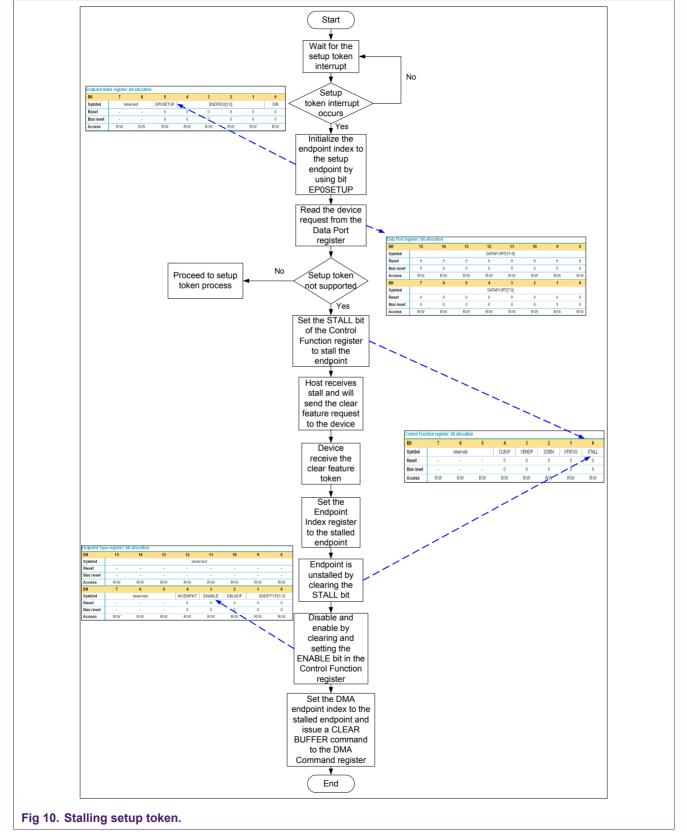

Besides these categories, there is also a stalling procedure for the endpoint (see <u>Section 3.4</u>). Special attention must be given when stalling the endpoint of the ISP1582/83.

The endpoint Index register is used to reference the control endpoint and the setup endpoint. The setup endpoint is 8 bytes in length. It is used for storing the USB peripheral request from the host. The firmware only needs to program the EPOSETUP bit of the ISP1582/83 (see <u>Table 10</u>:) to reference the index to the setup endpoint.

The data from the setup or control endpoint, indexed by the endpoint index is read from the FIFO using the Data Port register; see <u>Table 11</u>:.

| Bit       | 15  | 14  | 13  | 12     | 11       | 10  | 9   | 8   |

|-----------|-----|-----|-----|--------|----------|-----|-----|-----|

| Symbol    |     |     |     | DATAPC | RT[15:8] |     |     |     |

| Reset     | 0   | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

| Bus reset | 0   | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

| Access    | R/W | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| Bit       | 7   | 6   | 5   | 4      | 3        | 2   | 1   | 0   |

| Symbol    |     |     |     | DATAPO | DRT[7:0] |     |     |     |

| Reset     | 0   | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

| Bus reset | 0   | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

| Access    | R/W | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

|           |     |     |     |        |          |     |     |     |

#### Table 11: Data Port register: bit allocation

In the case of writing to the endpoint, the Data Port register is also used for the data transfer to the control IN endpoint. The control endpoint is controlled by the Control Function register (see <u>Table 12</u>:) that allows the firmware to clear the data in the OUT endpoint by using the CLBUF bit. The endpoint FIFO can be validated by either the Buffer Length register or the VENDP bit in the Control Function register. The Buffer Length register (see <u>Table 13</u>:) reflects the amount of data in the IN endpoint. As for the OUT endpoint FIFO, the buffer length is a means for the firmware to autovalidate the FIFO once the value is reached. It is used when the data to be sent in the IN endpoint is a short packet.

|           |     | on regiotori an |     |       |       |      |        |       |

|-----------|-----|-----------------|-----|-------|-------|------|--------|-------|

| Bit       | 7   | 6               | 5   | 4     | 3     | 2    | 1      | 0     |

| Symbol    |     | reserved        |     | CLBUF | VENDP | DSEN | STATUS | STALL |

| Reset     | -   | -               | -   | 0     | 0     | 0    | 0      | 0     |

| Bus reset | -   | -               | -   | 0     | 0     | 0    | 0      | 0     |

| Access    | R/W | R/W             | R/W | R/W   | R/W   | R/W  | R/W    | R/W   |

#### Table 12: Control Function register: bit allocation

#### Table 13: Buffer Length register: bit allocation

| Bit       | 15  | 14  | 13  | 12     | 11        | 10  | 9   | 8   |

|-----------|-----|-----|-----|--------|-----------|-----|-----|-----|

| Symbol    |     |     |     | DATACO | JNT[15:8] |     |     |     |

| Reset     | 0   | 0   | 0   | 0      | 0         | 0   | 0   | 0   |

| Bus reset | 0   | 0   | 0   | 0      | 0         | 0   | 0   | 0   |

| Access    | R/W | R/W | R/W | R/W    | R/W       | R/W | R/W | R/W |

| Bit       | 7   | 6   | 5   | 4      | 3         | 2   | 1   | 0   |

| Symbol    |     |     |     | DATACO | UNT[7:0]  |     |     |     |

| Reset     | 0   | 0   | 0   | 0      | 0         | 0   | 0   | 0   |

| Bus reset | 0   | 0   | 0   | 0      | 0         | 0   | 0   | 0   |

| Access    | R/W | R/W | R/W | R/W    | R/W       | R/W | R/W | R/W |

|           |     |     |     |        |           |     |     |     |

In the control function, the DSEN bit is for the ISP1582/83 to proceed to the data stage. If the setup token is with a data OUT stage, the firmware must set the DSEN bit to the ISP1582/83 for the device to generate an ACK handshake to the OUT endpoint. This bit also governs the IN endpoint data. An IN endpoint after a setup token with the data IN stage will not be sent to the USB bus even when the VENDP bit is issued. Therefore, the DSEN bit must be set for the ISP1582/83 to proceed to the status stage of the setup. The status stage is achieved by setting the STATUS bit in the Control Function register. On setting the STATUS bit, the endpoint will generate a zero-length packet to the IN token and send an ACK for the OUT token. The status stage will not generate the control IN endpoint interrupt.

## 3.3 Setup token with no data stage

## AN10039 ISP1582/83 Firmware Programming Guide

## 3.4 Stalling setup token

# 4. Mass storage application

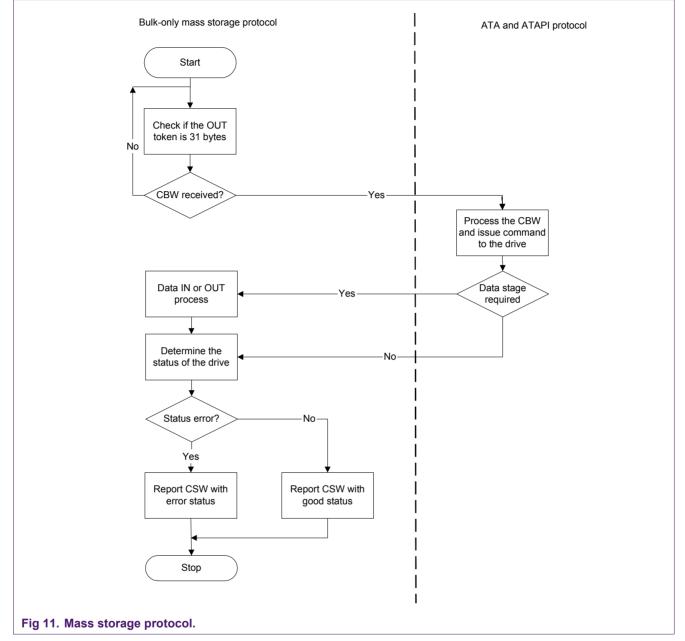

After successful enumeration, the respective device drivers come into play. For a mass storage application, the firmware must conform to the USB Mass Storage Class Bulk-Only Transport Specification and the ATA/ATAPI protocol. The host sends 31 bytes Command Block Wrapper (CBW). The ATAPI command is embedded in the CBW.

In the case of an ATAPI device, for each CBW received the ATAPI packet command is issued to the device, followed by the ATAPI command in the CBW.

In the case of an ATA device, the ATAPI command in the CBW must be translated into ATA command, before issuing to the device. The ATAPI command phase is followed by an optional data phase, which is followed by a status phase. If the command is successfully completed, the firmware has to report good status in the status field of the 13-byte Command Status Wrapper (CSW).

See <u>Table 14:</u> and <u>Table 15:</u> for CBW and CSW, respectively.

#### Table 14: Command Block Wrapper

| Bit                   | 7           | 6            | 5       | 4          | 3          | 2        | 1    | 0 |  |  |

|-----------------------|-------------|--------------|---------|------------|------------|----------|------|---|--|--|

| Byte                  |             |              |         |            |            |          |      |   |  |  |

| 30 to 15 (1Eh to 0Fh) |             |              |         | СВИ        | CBWCB      |          |      |   |  |  |

| 14 (0Eh)              |             | reserved (0) |         |            | L          | CBWCBLen | gth  |   |  |  |

| 13 (0Dh)              |             | reserv       | red (0) |            |            | bCB      | WLUN |   |  |  |

| 12 (0Ch)              |             |              |         | bmCBV      | VFlags     |          |      |   |  |  |

| 11 to 8 (0Bh to 08h)  |             |              | C       | dCBWDataTr | ansferLeng | th       |      |   |  |  |

| 7 to 4                |             |              |         | dCBV       | VTag       |          |      |   |  |  |

| 3 to 0                |             |              |         | dCBWSi     | ignature   |          |      |   |  |  |

| Table 15: Comman      | d Status Wr | apper        |         |            |            |          |      |   |  |  |

| Bit                   | 7           | 6            | 5       | 4          | 3          | 2        | 1    | 0 |  |  |

| Byte                  |             |              |         |            |            |          |      |   |  |  |

| 12 (0Ch)              |             |              |         | bCSW       | Status     |          |      |   |  |  |

| 12 (0Ch)             | bCSWStatus      |  |

|----------------------|-----------------|--|

| 11 to 8 (0Bh to 08h) | dCSWDataResidue |  |

| 7 to 4               | dCSWTag         |  |

| 3 to 0               | dCSWSignature   |  |

## 4.1 Mass storage protocol

## 4.1.1 Extracting Command Block Wrapper

- 1. Initialize the Endpoint Index register to the respective OUT endpoint.

- 2. Read the Buffer Length register. A buffer length of 31 indicates a command packet is in the buffer.

- 3. Read the Data Port register to extract the CBW.

- 4. Check for valid CBW signature in the command block.

If the CBW signature is valid, the command is issued to the ATA or ATAPI device.

For an invalid command block, the respective OUT endpoint is stalled.

© Koninklijke Philips Electronics N.V. 2005. All rights reserved

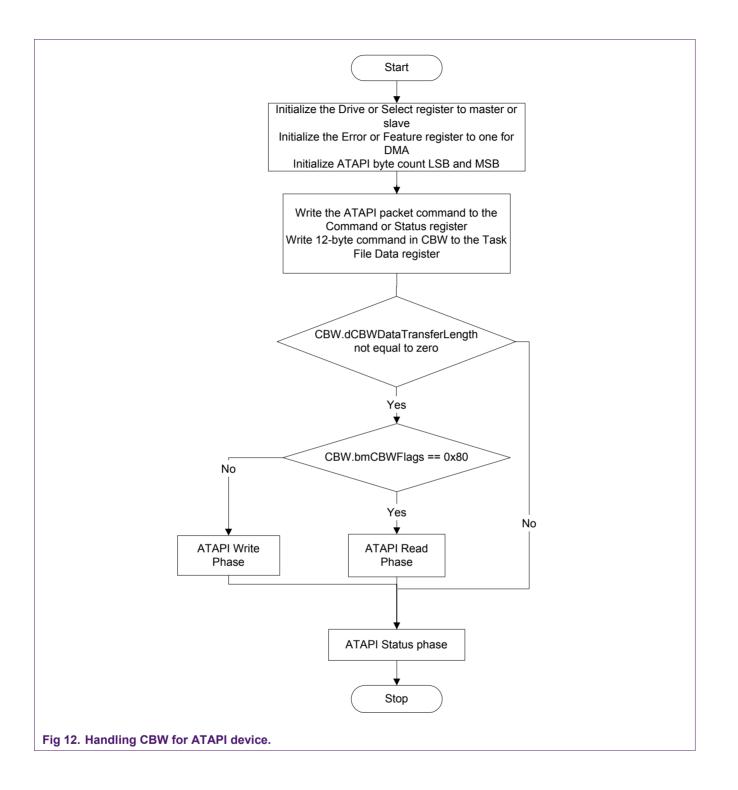

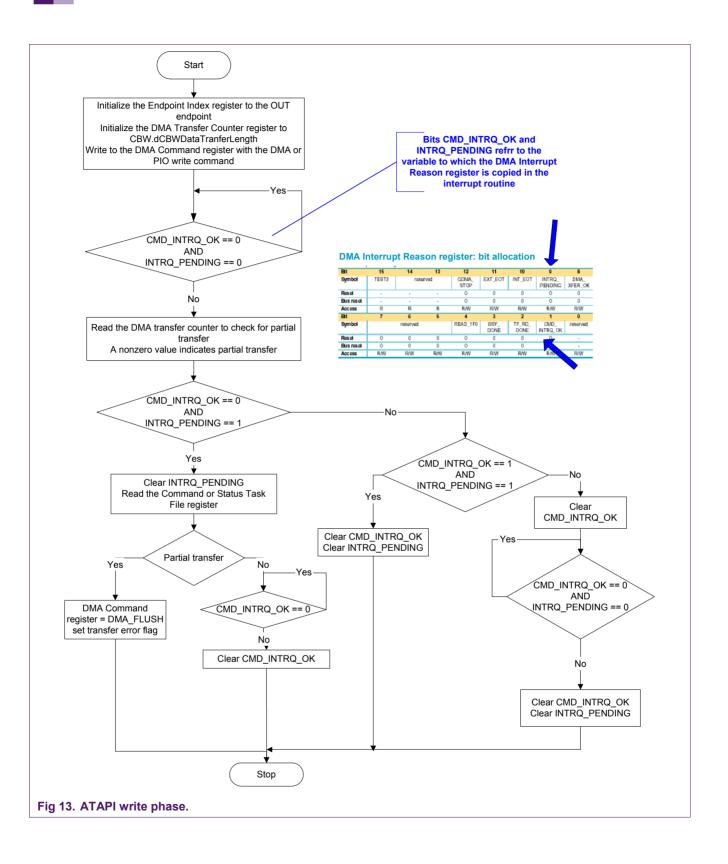

## 4.1.2 Handling CBW for ATA and ATAPI device

- 1. Initialize the drive select register (1F6) to the master or slave, based on the device present.

- 2. Initialize the Error or Feature register to 1 for a DMA transfer.

- 3. Initialize the ATAPI Byte Count LSB and ATAPI Byte Count MSB registers to the number of bytes to be transferred as specified in the CBW.

- 4. The ATAPI packet command is issued to the device by writing the Command or Status register.

- 5. Issue the 12-byte command block in CBW to the Task File Data register.

- 6. Check for the next phase.

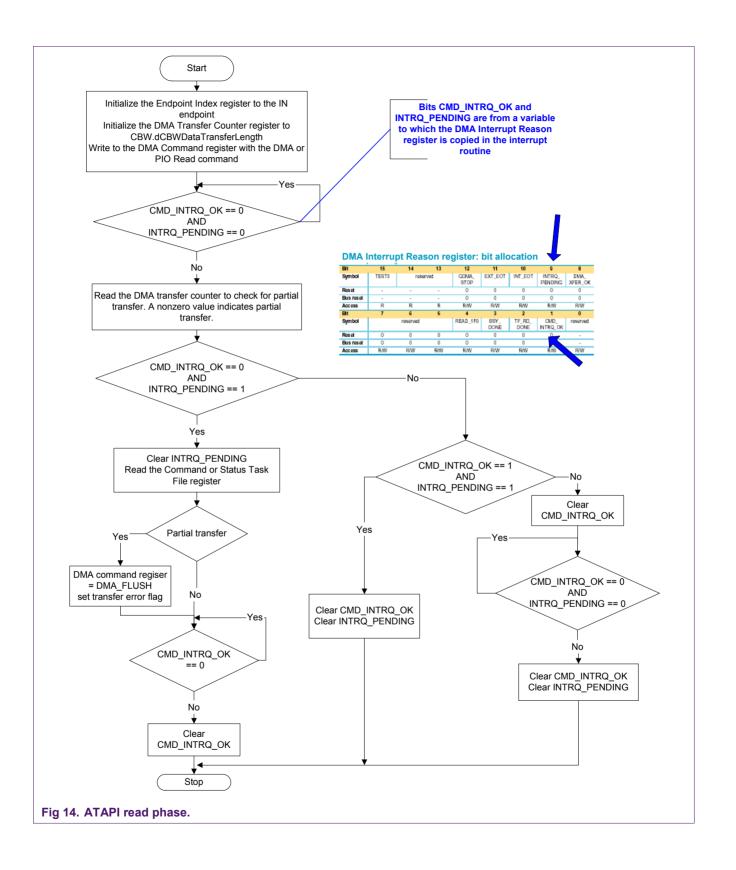

If CBW.dCBWDataTransferLength is zero, then the next phase is status. If CBW.dCBWDataTransferLength is non-zero and USB\_CBW.bmCBWFlags is 0x80, then the next phase is read. If CBW.dCBWDataTransferLength is non-zero and USB\_CBW.bmCBWFlags is not equal to 0x80, then the next phase is write.

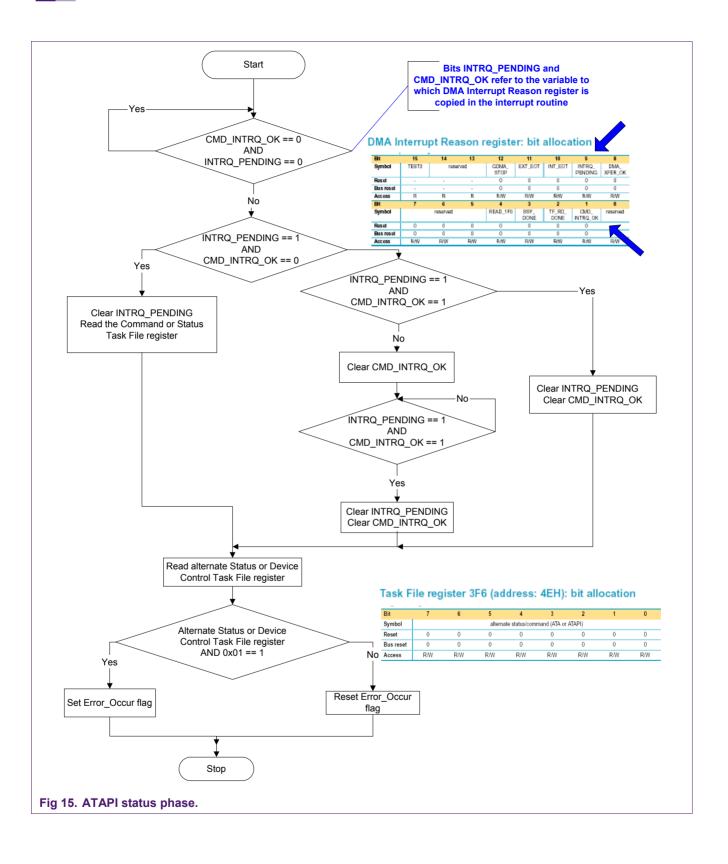

7. The read or write phase is followed by the status phase.

# ISP1582/83 Firmware Programming Guide

AN10039

## ISP1582/83 Firmware Programming Guide

## ISP1582/83 Firmware Programming Guide

## ISP1582/83 Firmware Programming Guide

## 4.1.3 Handling invalid CBW

A command block is invalid if it has an invalid CBW signature.

- 1. Initialize the Endpoint Index register to the respective OUT endpoint.

- 2. Set the STALL bit in the Control Function register. When the host receives a stall, it will send a clear feature command. Wait for the setup token interrupt for the clear feature.

- 3. Initialize the Endpoint Index register to the respective OUT endpoint, and clear the STALL bit in the Control Function register.

- 4. Set and reset the ENABLE bit in the Endpoint Type register. This will reset the data toggle.

- 5. Initialize the Endpoint Index register to 1 and set the STATUS bit in the Control Function register

- 6. Wait till the EP0Tx interrupt is received.

- 7. Wait for the EP0SETUP interrupt, for the bulk-only mass storage reset command.

- 8. Initialize the Endpoint Index register, by setting the EP0SETUP bit in the Endpoint Index register.

- 9. Read the Setup buffer and reinitialize the ATA or ATAPI device, for a valid mass storage reset command.

#### 4.1.4 Handling error

If the Error\_Occur flag or transfer\_error flag is set, error must be handled, by stalling the respective endpoint involved in the transfer.

- For the data OUT transfer, the respective OUT endpoint is stalled.

- For the data IN transfer, the respective IN endpoint is stalled.

- Clear the Error\_Occur and transfer\_error flag.

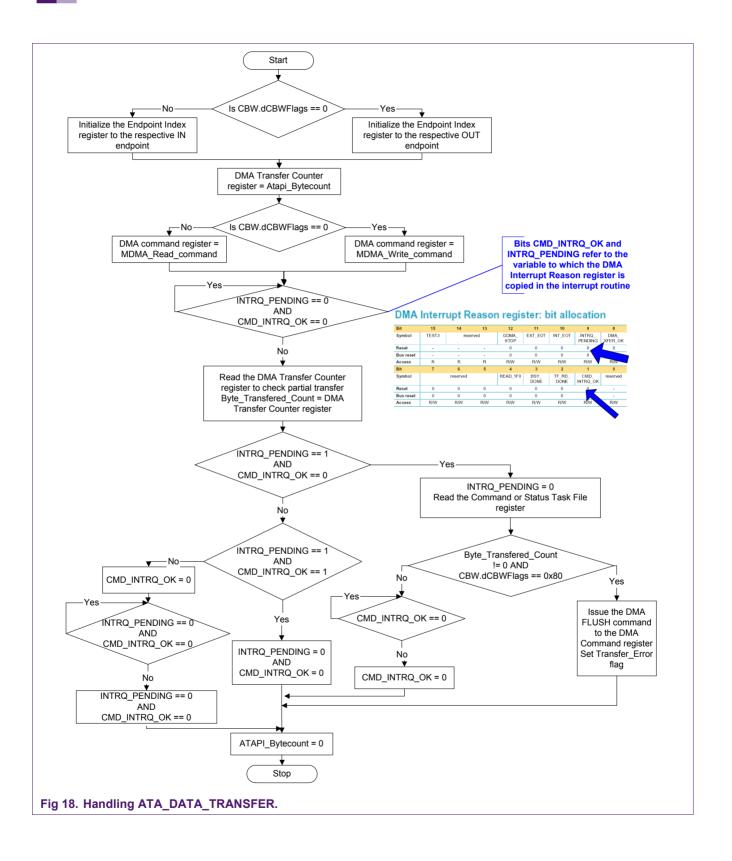

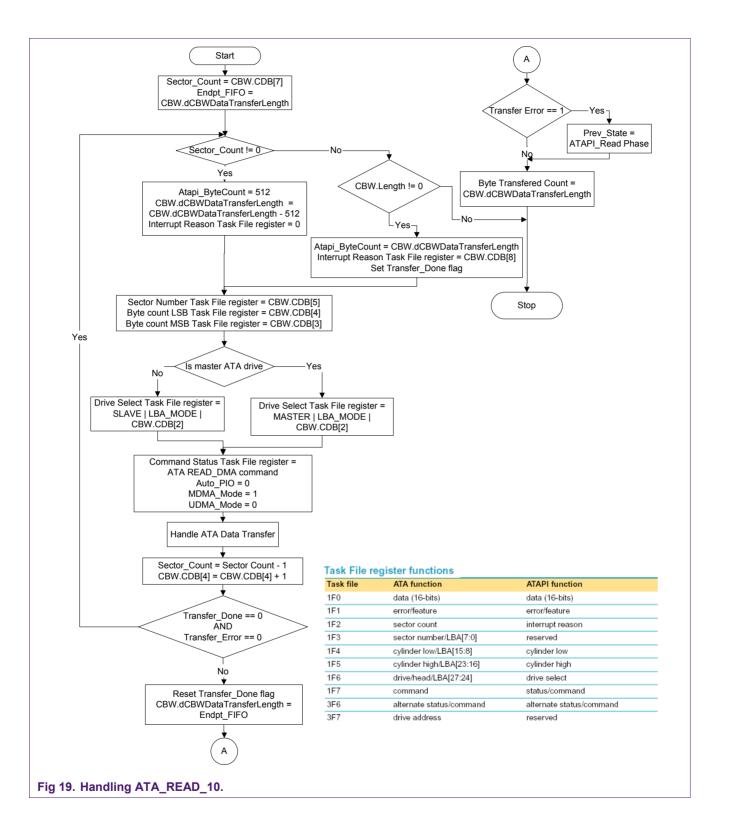

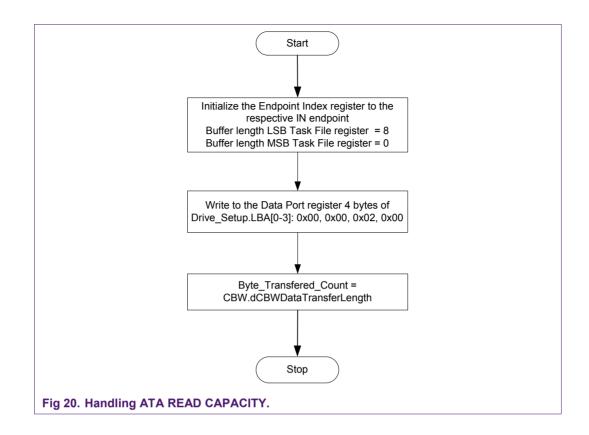

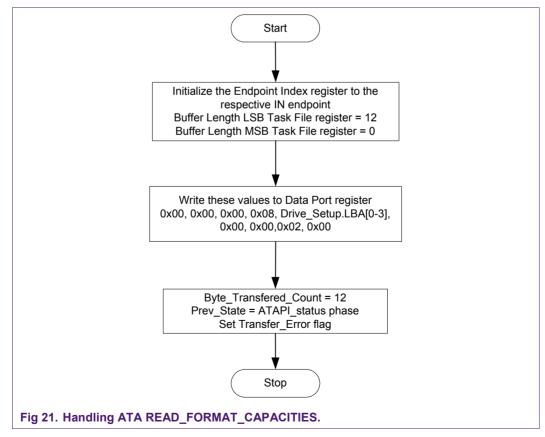

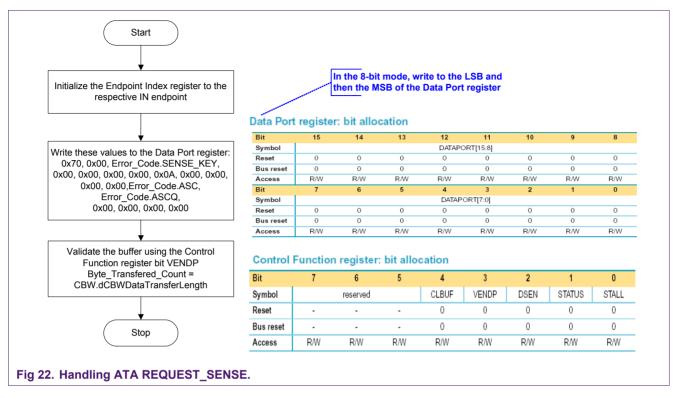

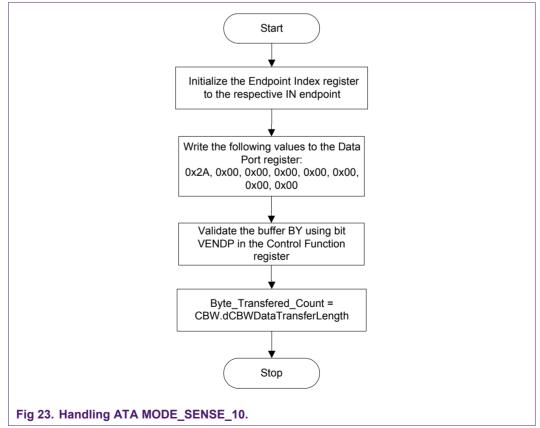

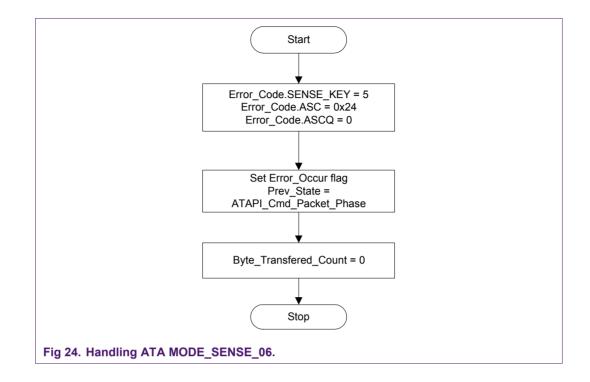

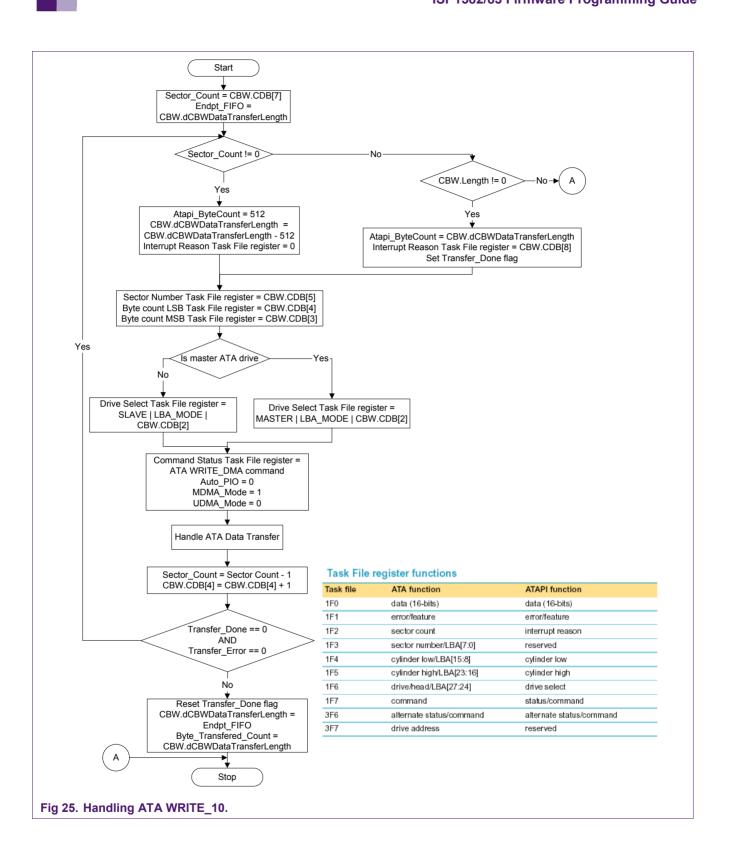

#### 4.1.5 Handling CBW for an ATA device

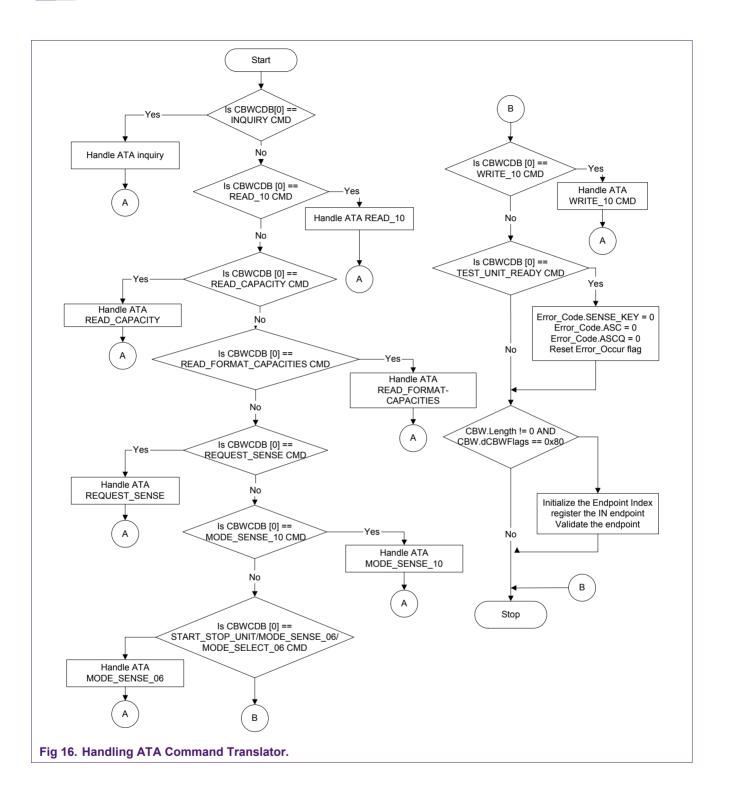

CBW contains the ATAPI command embedded in the command block.

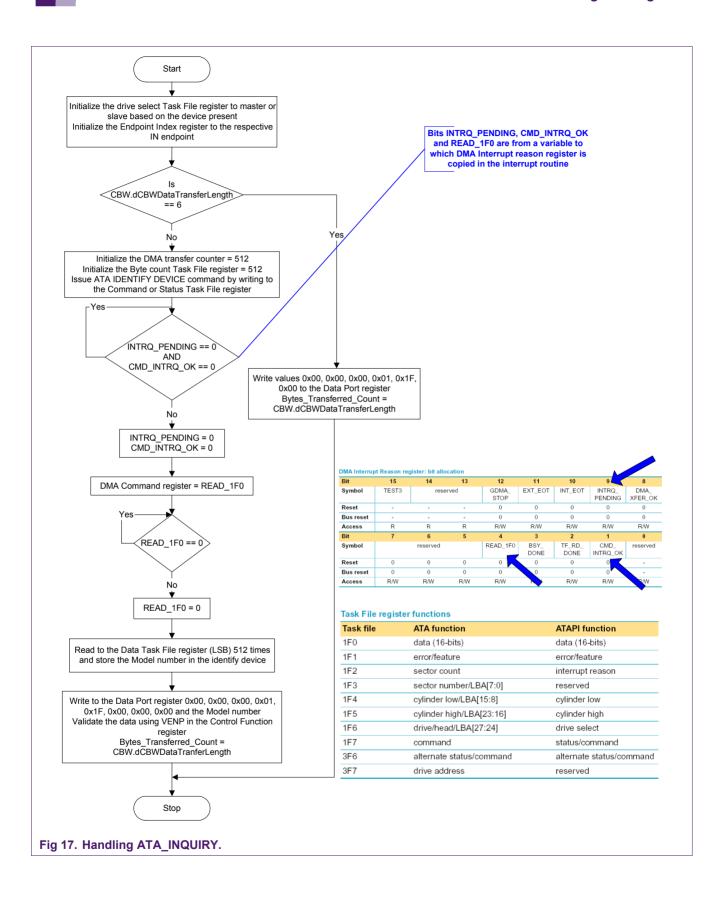

For an ATA device, the ATAPI packet command must be translated into an ATA command, before issuing to the device. The CBWCDB[0] field in the CBW contain the ATAPI command and the remaining field contains the command parameters. Based on the ATAPI command, the corresponding ATA command is selected and issued to the device.

#### ISP1582/83 Firmware Programming Guide

**V10039**

#### ISP1582/83 Firmware Programming Guide

# ISP1582/83 Firmware Programming Guide

# ISP1582/83 Firmware Programming Guide

AN10039

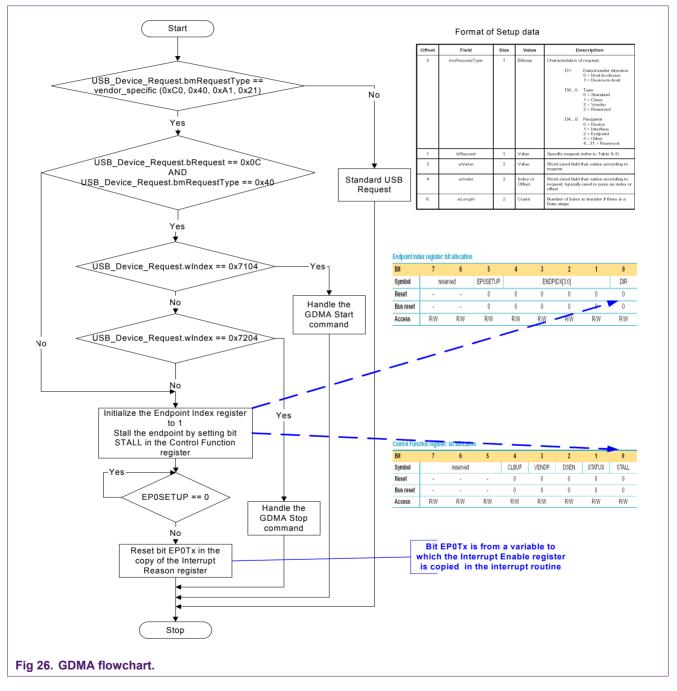

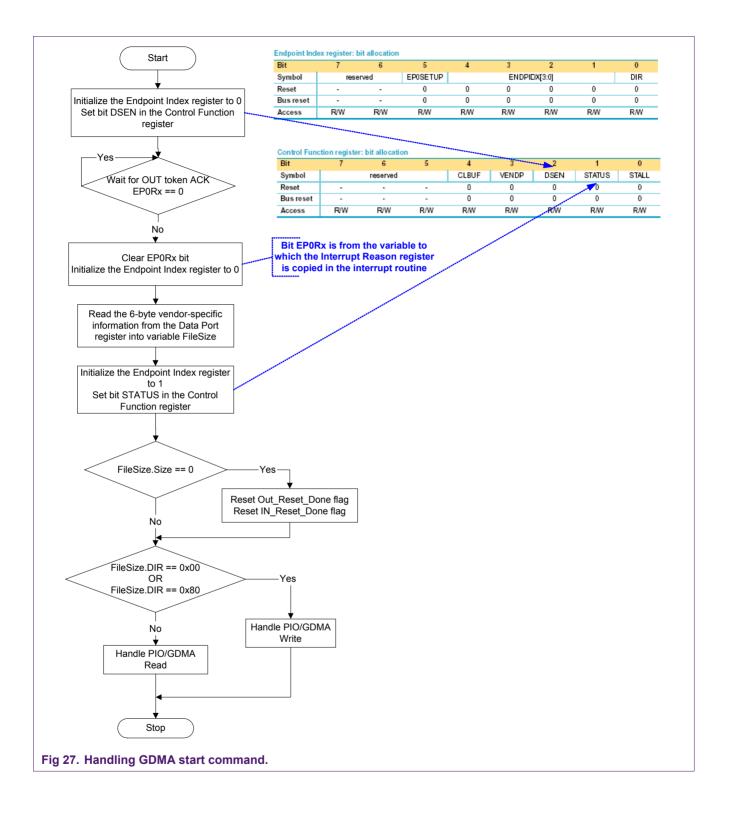

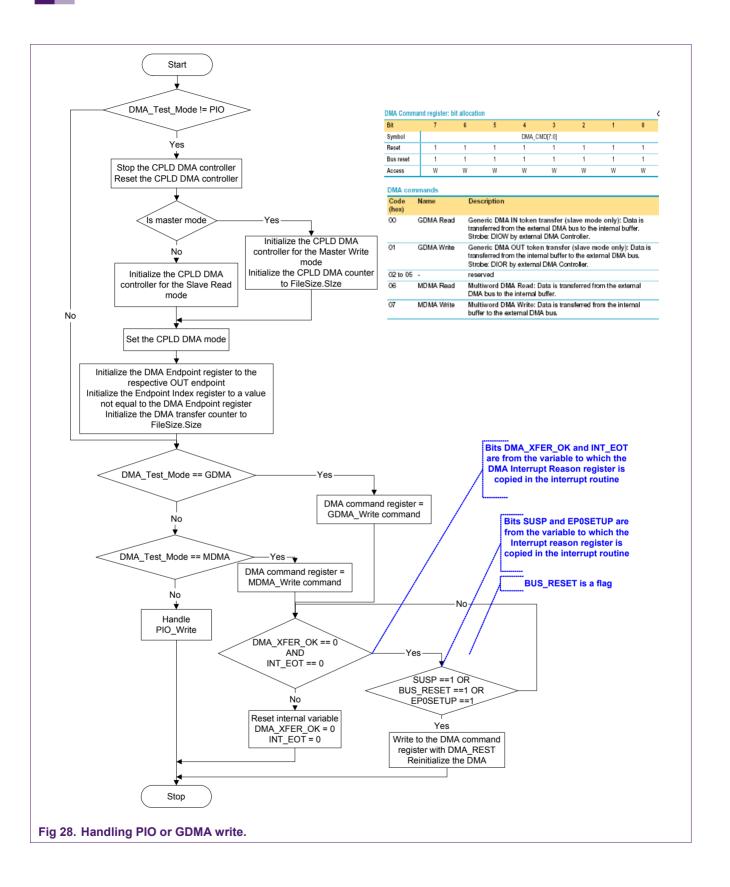

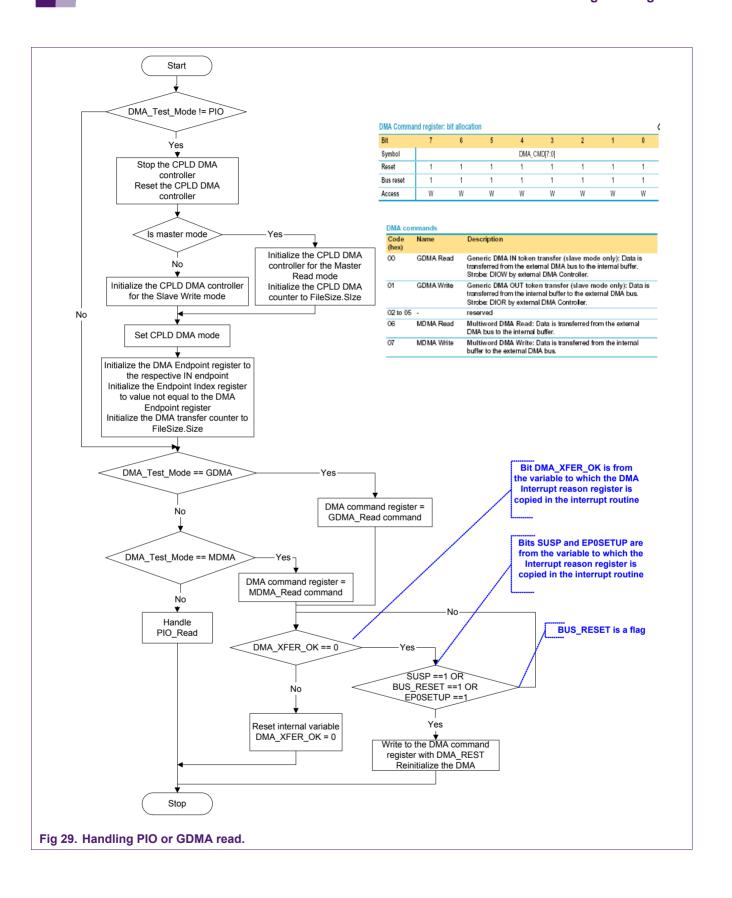

# 5. GDMA application

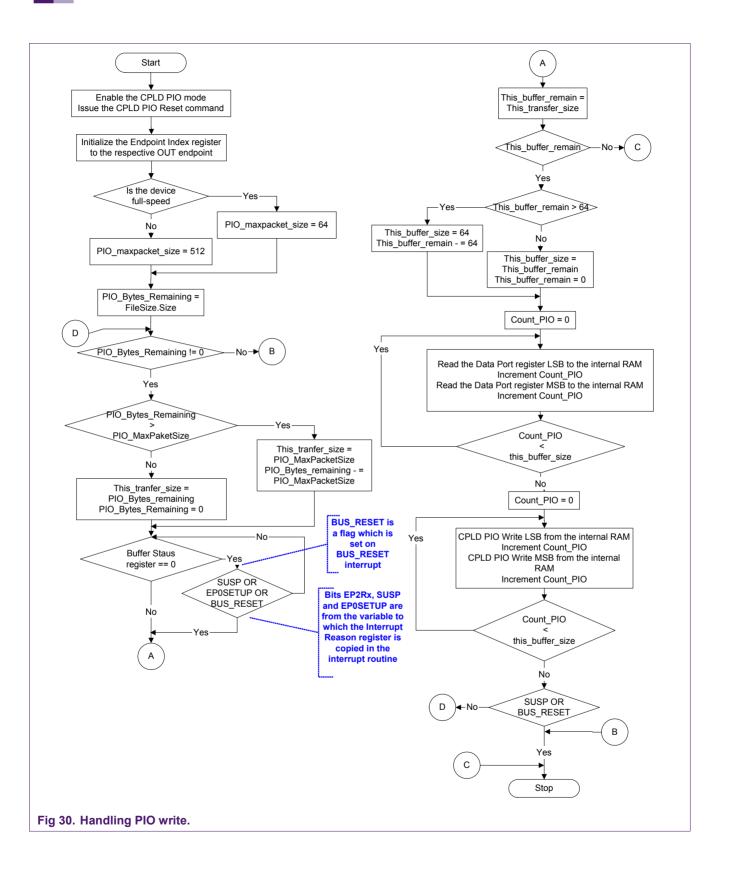

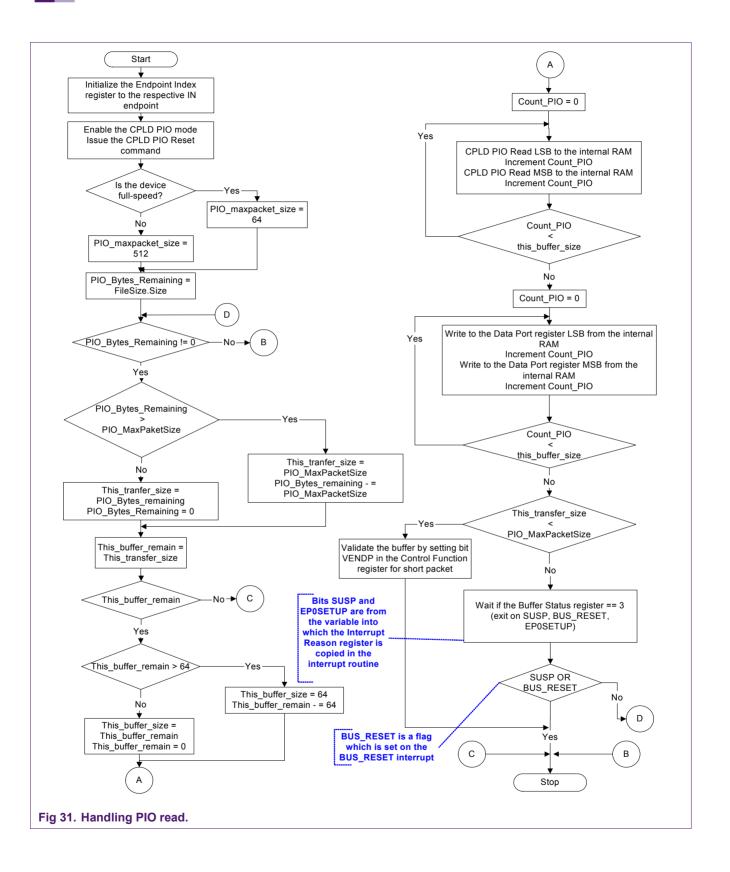

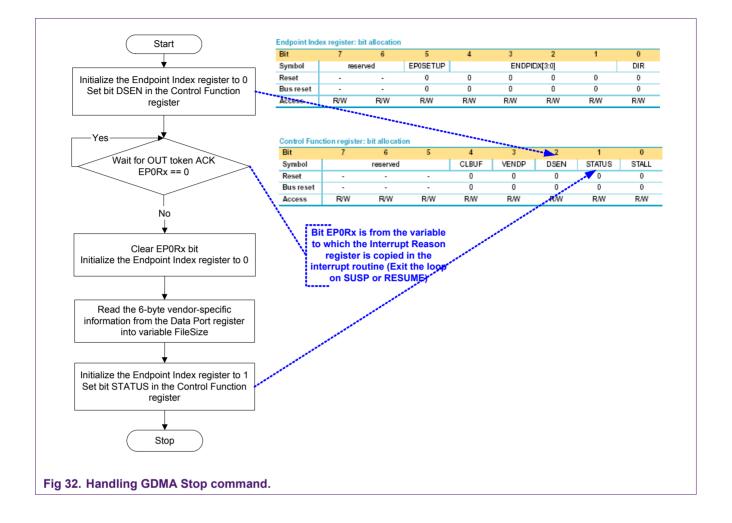

The GDMA application supports the GDMA slave and the PIO modes. These modes are selected based on the vendor-specific command issued by the host. The host sends an 8-byte setup packet, followed by a 6-byte vendor-specific information. The number of bytes to be transferred, the direction of transfer, and the mode of transfer are embedded in the vendor-specific command.

# ISP1582/83 Firmware Programming Guide

AN10039

# ISP1582/83 Firmware Programming Guide

110039

# ISP1582/83 Firmware Programming Guide

110039

## ISP1582/83 Firmware Programming Guide

## AN10039 ISP1582/83 Firmware Programming Guide

# 6. Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

**Right to make changes** — Philips Semiconductors reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no

responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

# 7. Trademarks

SoftConnect — is a trademark of Koninklijke Philips Electronics N.V.

© Koninklijke Philips Electronics N.V. 2005. All rights reserved

# 8. Contents

| 1.        | Introduction                                      | 3   |

|-----------|---------------------------------------------------|-----|

| 2.        | ISP1582/83 initialization routine                 | 4   |

| 2.1       | Initializing the ISP1582/83 registers             | 4   |

| 2.2       | Initializing the Mode register                    | 4   |

| 2.3       | Initializing the Interrupt Configuration register | 5   |

| 2.4       | Initializing the Interrupt Enable register        | 7   |

| 2.5       | Initializing the DMA Configuration and Hardwar    | e   |

| registers |                                                   |     |

| 2.6       | Initializing the ISP1582/83 endpoint              | 11  |

| 3.        | ISP1582/83 USB enumeration process                | 15  |

| 3.1       | Setup token with data IN stage                    | .17 |

| 3.2       | Setup token with data OUT stage                   | 18  |

| 3.3       | Setup token with no data stage                    | 19  |

| 3.4       | Stalling setup token                              | 20  |

| 4.        | Mass storage application                          | 21  |

| 4.1       | Mass storage protocol                             | 22  |

| 4.1.1     | Extracting Command Block Wrapper                  | 22  |

| 4.1.2     | Handling CBW for ATA and ATAPI device             | 23  |

| 4.1.3     | Handling invalid CBW                              | 28  |

| 4.1.4     | Handling error                                    | 28  |

| 4.1.5     | Handling CBW for an ATA device                    | 28  |

| 5.        | GDMA application                                  | 37  |

| 6.        | Disclaimers                                       | 44  |

| 7.        | Trademarks                                        | 44  |

| 8.        | Contents                                          | 45  |

#### © Koninklijke Philips Electronics N.V. 2005

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Date of release: 3 January 2005